# Harmonics compensation in Microgrid by using Fuzzy logic coordinate controller

Mr.J.T Ramalingeswar.,Asst.Prof , Department of EEE, SVCE,Tirupati. Email:ram.jt38@gmail.com P.Ashok(M.Tech), Department of EEE, SVCE, Tirupati. Email: puttuashok6@gmail.com Dr.RafiKiran., M.Tech.,Ph.D.,Prof& HOD , Department of EEE, SVCE,Tirupati. Email:rafikiran@gmail.com

#### **ABSTRACT**:

compensation In this paper the of neighborhood load harmonic current utilizing a single DG interfacing converter may make the intensification of supply voltage harmonics delicate burdens, especially when the fundamental grid voltage is very mutilated. Dissimilar to the op generation tion of unified power quality conditioners (UPOC) with arrangement converter, another harmonic current supply voltage and grid current harmonic pay methodology is proposed utilizing facilitated control of two shunt interfacing converters. In particular, the primary converter is in charge of neighborhood load supply voltage harmonic suppression. The second converter is utilized to alleviate the harmonic current created by the communication between the primary interfacing converter and the nearby nonlinear load. To understand a basic control of parallel converters, an altered mixture voltage and current controller is additionally created in the paper.

## **I. Introduction**

There are developing requests of utilizing power molding circuits in low and medium voltage control circulation system. Contrasting with massive detached filters that are very touchy to circuit parameters varieties, the dynamic power molding hardware including dynamic power filter (APF), dynamic voltage restorer (DVR), and unified power quality conditioner (UPQC) is favored due the quick element reaction and the great resistance to system parameter changes. Then again, the high entrance of distributed generation (DG) unit with power devices interfacing converter offers the likelihood of power appropriation system harmonic current compensation utilizing multi-utilitarian DG interfacing converter.

Past research predominantly centered around the control of a single DG shunt interfacing converter as an APF, as their energy devices circuits have comparative topology. To understand an upgraded dynamic separating objective, the ordinary current control techniques for grid tied DG interfacing converter might be adjusted. To start with, the wide data transfer capacity current controllers are utilized so that the frequencies of harmonic load current can fall into the transmission capacity of the present controller. On the other hand, the particular frequency harmonic pay utilizing multi-resounding current controller has gotten a consider generation measure of constrictions, as detailed. In the killjoy controller is created for different DG units with dynamic harmonic separating capacity. In the neural system strategy is utilized to enhance the harmonic separating execution of DG interfacing converters that are associated with a grid with substantial variety of grid impedance. Notwithstanding the pay of harmonics at low voltage dissemination arranges, the dynamic separating of music in higher voltage circulation system utilizing multi-level converters. Nonetheless, it is critical to note that previously mentioned compensation strategies are primarily utilized as a part of grid tied converter systems. In late writing, the hybrid voltage and current control is likewise created to

understand a fundamental voltage control for DG control direction and a harmonic current control for nearby load harmonic compensation. Contrasted with the previously mentioned customary current control strategies, the crossover controller permits an interfacing converter to repay music in both network tied and islanding micro grids with help of the low transmission capacity interchanges between DG units, it likewise harmonic extraction to accomplish harmonic power sharing among parallel DG systems.

#### **II. Review of Conventional APF and DVR**

This area quickly audits the control of shunt APFs for network current harmonic alleviation and arrangement DVRs for supply voltage harmonic suppression. To contrast and the proposed parallel-converter utilizing adjusted half and half voltage and current controller as appeared in the following segment, the surely knew double-loop current control and voltage control are connected to APFs and DVRs, individually.

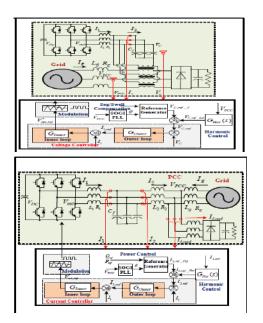

Fig.1. Diagram of local harmonic compensation using interfacing converter

# A. Shunt Interfacing Converters for Grid Current Harmonic Mitigation

Fig. 1(a) demonstrates the topology and control system of an interfacing converter for compensating generation ting harmonic current from a neighborhood nonlinear load. To start with, the neighborhood load is associated with the output of the interfacing converter, and afterward, they are coupled to the primary network through the grid feeder. The parameters of the interfacing converter LCL filter and the network feeder are recorded as z1(s) =sL1 + R1, z2(s) = sL2 + R2, z3(s) = 1/(sCf), and zg(s) =sLg + Rg, where L1, L2, R1, and R2 are the inductance and resistance of the filter arrangement stifles, Cf is the capacitance of the shunt capacitor, and Lg and Rg are grid inductance and resistance.

The present control plan is appeared in the lower some portion of Fig. 1(a). As per the customary APF control hypothesis, the neighborhood stack current is measured and the harmonic segments are distinguished as:

$$I_{2,ref_h} = H_{Har}(s) \cdot I_{Load} \tag{1}$$

Where *HHar* (*s*) is the exchange capacity of the harmonic segment indicator and *ILoad* is the nearby load current.

At the point when both the key and the harmonic parts are resolved, the reference current is acquired as I2, =  $I2,_f + I2, ref_h$  and it is utilized as the contribution for a double-loop line current I2 control.

$$I_{l,ref} = H_{Outer}(s) \cdot (I_{2,ref} - I_2)$$

$$V_{out,ref}^* = H_{Inner}(s) \cdot (I_{1,ref} - I_1)$$

(2)

(3)

Where *HOuter* (s) and *HInner* (s) are the controllers of the external and the internal control loops, separately. *I*1, and *I*1 are the reference and the quick inverter output current, separately. *Vout*, \* is the output voltage reference of the inverter.

# **B.** Series Interfacing Converters for Supply Voltage Harmonic Mitigation

It is important generation to note that notwithstanding when the harmonic current of shunt nonlinear burdens is adjusted, the supply voltage to neighborhood load is not gen generation simply sinusoidal. This can be brought on by a couple reasons including the fundamental system voltage consistent state harmonic bends. Assume the system current Ig in Fig. 1(a) is without swell, the harmonic voltage drop on the grid feeder Rgand Lg is zero. For this situation, the harmonic voltage at PCC is the same as the harmonics from the principle network. To address the previously mentioned issue, an arrangement DVR can be introduced as appeared in Fig. 1(b), where the system is combined with the power distribution arrange arrangement utilizing an associated coordinating

transformer. The auxiliary of the transformer is associated with a converter with output LC filter.

To begin with, the PCC voltage is measured by the DVR controller and the central and harmonic PCC voltage segments are isolated. At that point, the supply voltage harmonic parts are repaid by setting up the harmonic voltage reference of the DVR as  $Vref_h = VPCC_h$  and the basic voltage reference  $Vref_f$  of the DVR is resolved by the droop and swell compensation necessity of the system [3].

At the point when the central and harmonic part references are resolved, the DVR reference voltage is gotten as VC, = VC,  $_f + VC$ ,  $ref_h$ . A while later, a double-loop voltage control is connected to guarantee a quick voltage

$$I_{1,ref} = H_{Outer}(s) \cdot (V_{C,ref} - V_C)$$

<sup>(4)</sup>

(5)

following as

Where *HOuter* (s) and *HInner* (s) are the controller of the external and the inward control loops, separately. , and *VC* are the reference and the immediate estimation of DVR voltage, separately.

# III. THE PROPOSED COORDINATED CONTROL METHOD

$\boldsymbol{V}_{\textit{out,ref}}^{*} = \boldsymbol{H}_{\textit{Inmer}}(\boldsymbol{s}) \cdot (\boldsymbol{I}_{\textit{1,ref}} - \boldsymbol{I}_{\textit{1}})$

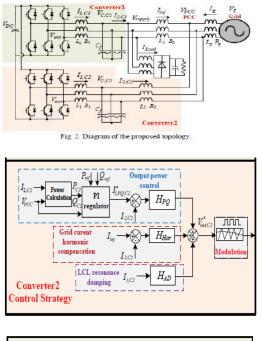

To have harmonic current alleviation of the supply voltage and the grid current harmonics, a compensation technique utilizing facilitated control of two parallel interfacing converters is proposed in this segment. The hardware and control outlines of the proposed system are appeared in Fig. 2 and Fig. 3, individually. Initial, a DG unit with two parallel interfacing converters having a similar DC rail is associated with PCC. Each interfacing converter has a output LCL filter and the nearby nonlinear load is put at the output filter capacitor of converter1. In this topology, the supply voltage to neighborhood nonlinear load is upgraded by controlling the harmonic part of interfacing converter1. In the interim, the network current harmonic is relieved by means of the power molding through interfacing converter2. Their definite control systems are talked about separately, as demonstrated as follows:

#### A. Control Strategy for Converter

To start with, the line current I2,1 of converter1 and the PCC voltage *VPCC* as appeared in Fig. 2 are measured to compute the genuine and receptive output

power of this converter

$$\begin{cases}

P_{C1} = \frac{3\tau}{2(s+\tau)} (V_{PCC,\alpha} \cdot I_{2\alpha,C1} + V_{PCC,\beta} \cdot I_{2\beta,C1}) \\

Q_{C1} = \frac{3\tau}{2(s+\tau)} (V_{PCC,\beta} \cdot I_{2\alpha,C1} - V_{PCC,\alpha} \cdot I_{2\beta,C1}) \\

\end{cases}$$

(6)

where *PC*1 and *QC*1 are the output genuine and receptive power of converter1, *VPCC*,  $\alpha$  and *VPCC*,  $\beta$  are the PCC voltage in the two-hub stationary reference outline, and *I*2 $\alpha$ , *C*1 and *I*2 $\beta$ , *C*1 are the line current of converter1, and is the time  $\tau$  constant of low pass filters. The time steady of the low pass filter is for the most part controlled by two components. To begin with, the genuine and receptive power swells brought on by line current music must be appropriately sifted through. Besides, the quick element control should be kept up. As per the outline rule.

Fig.3. Diagram of the proposed interfacing converter control strategies

Special Issue-5 ISSN: 2349-6495(P) | 2456-1908(O)

Note that the power reference is gen generation decided by the accessible power from the back phase of the DG unit. At the point when there is vitality stockpiling system in the DG unit, the power reference can likewise be controlled by the vitality administration arrangement of a DG unit or a micro grid. Along these lines, for straightforwardness, the harmonic pay administration is typically initiated when there is adequate power rating in the interfacing converters. The output of the power reference gen generation tor is the line current reference  $I2_{...,1}$

$I_{2,PQ,C1}^{*} = g_{P} \cdot (V_{PCC,\alpha} + jV_{PCC,\beta})$  $+ g_{Q} \cdot (V_{PCC,\beta} - jV_{PCC,\alpha})$  (7)

Where gp and gQ are two customizable additions that can control converter1 output genuine and receptive power, separately. This controller just uses a duplicate of the momentary PCC voltage vector (, -+ -- --, --) and the conjugated part as the present reference. This depends on a reality that the genuine output power is in extent to the line current -2 that outsiders to immediate PCC voltage vector, while the receptive power is corresponding to the line current that outsiders to the conjugated PCC vector -- -- --, as appeared in Fig. 4.

The additions  $\Box \Box$  and  $\Box \Box$  in are controlled by two PI controllers as

$$\begin{cases} g_p = (k_{p_p PQ} + \frac{k_{i_p PQ}}{s}) \cdot (P_{ref} - P_{C1}) \\ g_q = (k_{p_p PQ} + \frac{k_{i_p PQ}}{s}) \cdot (Q_{ref} - Q_{C1}) \end{cases}$$

(8)

Where k and and are PI controller coefficients.

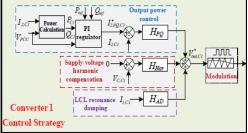

Customarily, the half and half controller in controls the DG key voltage for power control and the harmonic current for

load harmonic current relief. As this converter is in charge of repaying harmonic parts of the supply voltage, the controllers in the half breed voltage and current controller is changed with harmonic supply voltage control and central line current control as:

$$V_{out,C1}^{*} = H_{PQ}(s) \cdot (I_{2,PQ,C1}^{*} - I_{2,C1}) + Voltage Harmonic Mitigation Active Damping (9) H_{Har}(s) \cdot (V_{C,C1}^{*} - V_{C,C1}) + H_{AD}(s) \cdot I_{1,C1}$$

where  $\Box \Box \Box \Box$ ,  $\Box 1 *$  is reference voltage for PWM preparing,  $\Box 2, \Box, \Box 1 *$  is the line current reference of the Power Control term,  $\Box \Box, \Box 1 *$  is the reference voltage of the Voltage Harmonic Mitigation term,  $\Box \Box, \Box 1$  is the filter capacitor voltage, and  $\Box 1, \Box 1$  is the converter 1 output current. As appeared in Fig. 2, the filter capacitor voltage ( $\Box \Box, 1$ ) is the same as the heap voltage ( $\Box \Box \Box \Box \Box \Box$ ). The controllers of the Power Control, Voltage Harmonic Mitigation and Active Damping terms are recorded as

$$\begin{split} H_{pQ}(s) &= k_{p1,C1} + \frac{2\kappa_{i,f,C1}\omega_{c}s}{s^{2} + 2\omega_{c}s + \omega_{o}^{2}} \end{split} \tag{10} \\ H_{Har}(s) &= k_{p2,C1} + \sum_{h=5,7,11,13} \frac{2k_{\nu,h,C1}\omega_{c}s}{s^{2} + 2\omega_{c}s + (h \cdot \omega_{o})^{2}} \\ H_{AD}(s) &= k_{AD,C1} \end{aligned} \tag{12}$$

where  $\Box \Box, \Box \Box$  is the relative pick up and  $\Box, \Box, \Box$  is the thunderous controller pick up for the power control controller  $\Box \Box \Box \Box$  ( $\Box$ ),  $\Box \Box Z, \Box \Box$  is the corresponding addition and  $\Box, h, \Box \Box$  is the full controller pick up for the voltage harmonic relief controller  $\Box \Box \Box \Box$ , and  $\Box \Box, \Box \Box$  is the relative control that can effectively stifle the LCL filter reverb generation .

It is important to note that lone the essential relative additions  $\Box \Box 1,1$  and  $\Box \Box 2,\Box 1$  is much lower than the full controller pick up  $\Box \Box,h,\Box 1$ . Accordingly, the output of the Power Control term in (9) has low harmonic part. Because of this element, the contorted network voltage can be straightforwardly utilized as the contribution of (7), as its harmonic part can be naturally sifted through by (10). In the meantime, it can be seen that the output of the second Voltage Harmonic Mitigation term just has low major parts, as just resounding controllers at the chose harmonic frequencies are received in the control term. Accordingly, the Power Control term and Voltage Harmonic Mitigation term are exceptionally all around decoupled. As needs be, an interfacing converter can dispatch energy to the system and repay supply voltage music in the meantime.

Furthermore, dissimilar to the routine DVR with PCC harmonic voltage extractions, the Voltage Harmonic Mitigation term can understand dynamic supply voltage harmonics compensation with no harmonic extractions. What's more, it can be seen that a shut circle control is acknowledged without utilizing stage bolted loops.

At last, it is important to accentuation that contrasting with the customary half breed controller that uses the hang control to acknowledge mod generation mod generation power control flow, the principal current control in (9) could successfully enhance the power control dynamic reaction.

#### A. Control Strategy for Converter2

The control procedure of converter2 is like that of converter1, as additionally exhibited in Fig. 3. Be that as it may, both the fundamental and the harmonic converter streams are controlled. In the first place, the controllers as appeared in (6) to (8) are embraced to get the power control term reference 22, 1 and 22, 1 are the line current of converter1, and  $\tau$  for converter2. Subsequently, another mixture controller is utilized to understand the shut circle line current control of conveter2 as:

$$V_{out,C2}^* = H_{PQ}(s) \cdot (I_{2,PQ,C2}^* - I_{2,C2}) +$$

Current Harmonic Mitigation Active Damping

$$H_{Har}(s) \cdot (I_{2,Har,C2}^* - I_{2,C2}) + H_{AD}(s) \cdot I_{1,C2}$$

(13)

where  $\Box \Box \Box, \Box 2 *$  is reference voltage for converter2 PWM handling,  $\Box 2, \Box, \Box 2 *$  is the present reference for converter2 control,  $\Box 2, \Box, \Box 2 *$  is the present reference for converter2 line current harmonic control,  $\Box 1, \Box 2$  is the converter2 output current. The controllers of Power Control, Current Harmonic Mitigation and Active Damping terms are recorded here as

$$H_{pQ}(s) = k_{p1,C2} + \frac{2k_{i,f,C2}\omega_c s}{s^2 + 2\omega_c s + \omega_o^2}$$

(14)

$$H_{Har}(s) = k_{p2,C2} + \sum_{h=5,7,11,13} \frac{2k_{i,h,C2}\omega_c s}{s^2 + 2\omega_c s + (h \cdot \omega_o)^2}$$

(15)

$$H_{AD}(s) = k_{AD,C2}$$

(16)

. Similar to converter1, the Power Control term and the Current Harmonic Mitigation term are exceptionally very much decoupled. In this manner, PLLs is a bit much and the contribution of Power Control term  $\Box_{2,2} *$  can have a few bends when utilizing an immediate duplicate of PCC voltage. Moreover, take note of that the distinction between the converter1 line current and the heap current  $\Box \Box \Box$  (found in Fig. 2, equivalents to  $\Box_{2,1} - \Box \Box \Box$ ) is received as the contribution of Current Harmonic Mitigation term of converter2 as  $\Box_{2,\Box} \Box_{,\Box} \Box_{,Z} * = \Box \Box \Box_{,\Box}$ . As just harmonic full controllers are utilized as a part of the Current Harmonic Mitigation term and the corresponding increase  $\Box_{2,2}$  is much littler than  $\Box_{,h,\Box}2$  in (15), converter2 can effectively compensating generation the harmonic current from converter1 with no harmonic current recognition. For this situation, the infused current  $\Box$  to the primary network is harmonic free.

In rundown, the proposed topology and the altered cross breed controller can understand an upgraded nature of supply voltage to the neighborhood stack and the grid current to the primary system in the meantime. Through the organized control of two parallel converters, the previously mentioned control quality change target is acknowledged in a computationally compelling way, without including any PLLs and harmonic voltage/current extractions in the whole procedure. What's more, when the principal current direction in the Power Control term in (13) and (9) is supplanted by the surely knew hang control for major voltage control, the proposed technique can be utilized as a part of an islanded micro grid in a comparative way.

#### **C. Frequency Domain Analysis**

As both converter1 and converter2 have frequency specific element at the major and they chose harmonic frequencies, the supply voltage harmonic and system current harmonic compensation execution can be analyzed by frequency area investigation utilizing Bode plots. Initial, a LCL filter of a converter is appeared in Fig. 5, where the neighborhood load is disentangled as a harmonic current source associated with the shunt capacitor of converter LCL filter. The reaction of the filter plant is given as

$$(\frac{V_{out}}{z_1} + \frac{V_{PCC}}{z_2} - I_{Load}) \cdot (\frac{1}{z_1} + \frac{1}{z_2} + \frac{1}{z_c}) = V_C$$

$$(17)$$

$$V_{out} - V_C = z_1 \cdot I_1$$

$$V_C - V_{PCC} = z_2 \cdot I_2$$

$$(19)$$

In light of the control methodologies in (9) and (13), the exchange capacity of the LCL filter circuit (see (17) to (19))

for both converter1 and converter2, and expecting that  $\Box \Box \Box$ ,  $\Box 2 * = \Box \Box t$ ,  $\Box 2$  and  $\Box \Box \Box$ ,  $\Box 1 * = \Box \Box \Box$ ,  $\Box 1$ , the shut circle current and voltage reaction of parallel converters can be set up as  $V_{C,C1} = R_{11}(s)V_{C,C1}^* + R_{12}(s)I_{2,PQ,C1}^* - R_{13}(s)I_{2,C1}$  (20)

$$I_{2,C1} = R_{21}(s)V_{C,C1}^* + R_{22}(s)I_{2,PQ,C1}^* + R_{13}(s)V_{PCC}$$

(21)

$$I_{2,C2} = R_{31}(s)I_{2,PQ,C2}^* + R_{32}(s)I_{2,Har,C2}^* - R_{33}(s)V_{PCC}$$

(22)

Where the coefficients  $\Box 11(\Box)$  to  $\Box 33(s)$  in portray the reaction of these two converters to different excitations of the system. In particular, (20) predominantly centers the execution of converter1 at harmonic frequencies, while expects to depict the execution of the system at around basic frequency. As it were, converter1 has voltage source trademark at harmonic frequencies however current source trademark at around the essential frequency. Then again, as both essential and harmonic line current are controlled for converter2, just a single current source proportional circuit in can be utilized to show the execution of converter2. With a specific end goal to make the examination more direct, a mind boggling circuit arrange as appeared in Fig. 6 is produced to show how the harmonic voltage and current harmonic are at the same time adjusted. Take note of that this identical circuit arrange in Fig. 6 is just viable at the chosen harmonic frequencies.

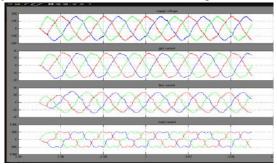

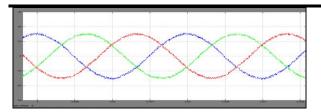

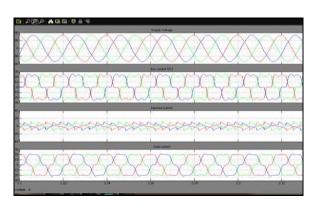

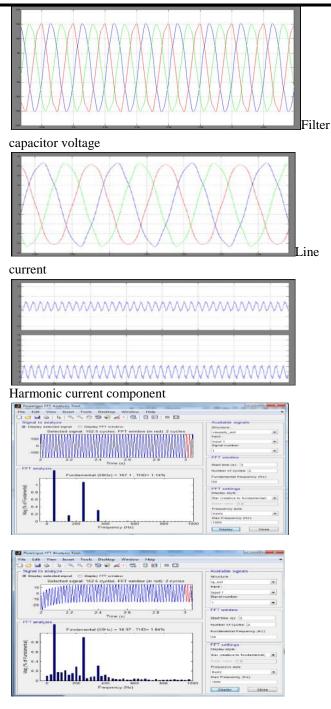

Fig.11. only the local load harmonic current is compensated. (From upper to lower: 0000, 00, 02, 0000)

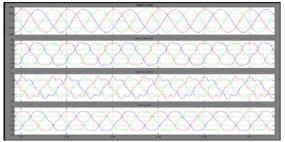

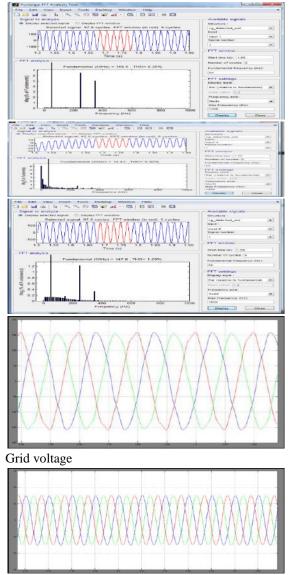

Fig.12. The harmonic spectrum of grid current  $\Box$

Fig.13. the harmonic spectrum of supply voltage

Fig.15. The harmonic spectrum of grid current  $\Box$

Fig.16. The harmonic spectrum of supply voltage

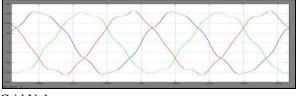

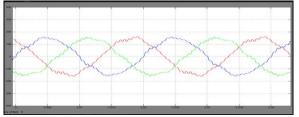

Grid Voltage

### Special Issue-5 ISSN: 2349-6495(P) | 2456-1908(O)

### Grid Current

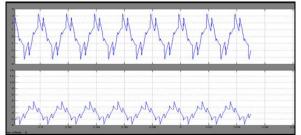

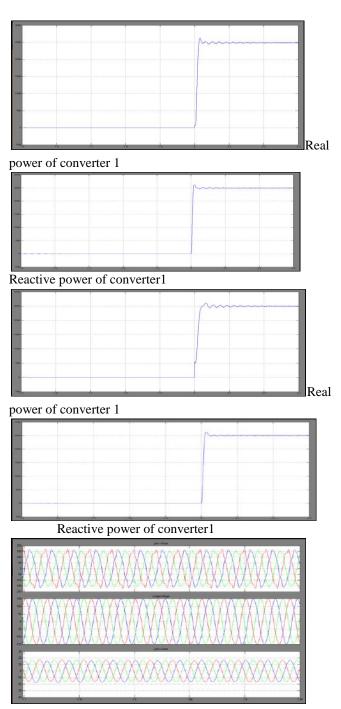

Fig.18. Performance of converter1. (From upper to lower:

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□

□</

Filter Capacitor Voltage

Harmonic Current Component

Fig.21. The harmonic spectrum of supply voltage

### Fig.20. The harmonic spectrum of grid current $\Box$ $\Box$

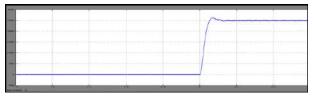

Fig. 22. Real and reactive power of converter1 and converter2

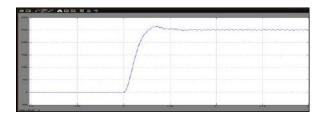

Fig. 23. The performance of the dual-converter system during 10% grid voltage sags, with 10.03% THD **Fuzzy logic Controller**

Fuzzy technique for thinking is a kind of different respected avocation in which reality estimations of factors might be any true blue number some place around 0 and 1. By partition, in Boolean strategy for thinking, reality estimations of factors may just be 0 or 1. Fuzzy technique for thinking has been reached out to handle the likelihood of halfway truth, where reality quality may extend between completely certifiable and totally false. Moreover, when etymological factors are utilized, these degrees might be managed by particular points of confinement.

Routinely Fuzzy technique for thinking control structure is delivered utilizing four immense sections showed on Figure fuzzification interface, Fuzzy insincerity motor, cushy standard system and Defuzzification interface. Every part near to foremost Fuzzy strategy for thinking operations will be depicted in more detail below.

The Fuzzy technique for thinking examination and control approachs appeared in Figure 1 can be depicted as:

1. Receiving one or sweeping number of estimations or other assessment of conditions existing in some system that will be investigated or controlled.

2. Processing all got contributions as appeared by human based, Fuzzy "expecting then" models, which can be granted in fundamental dialect words, and joined with normal non-Fuzzy arranging.

3. Averaging and weighting the outcomes from all the individual norms into one single yield choice or sign which picks what to do or urges a controlled system what to do. The outcome yield sign is an exact defuzzified respect. Most importantly else, the unmistakable level of yield (fast, low speed et cetera.) of the stage is described by deciding the cooperation capacities with respect to the fuzzy sets.

#### **Fuzzy Logic System**

Today control systems are normally portrayed by numerical models that take after the laws of material science, stochastic models or models which have risen up out of scientific rationale. A general trouble of such built model is the manner by which to move from an offered issue to an appropriate numerical model. Without a doubt, today's propelled PC innovation makes it conceivable; however overseeing such systems is still excessively perplexing. These perplexing systems can be rearranged by utilizing a resilience edge for a sensible measure of imprecision, dubiousness and instability amid the demonstrating stage. As a result, not totally consummate system comes to presence; by and by in the greater part of the cases it is equipped for taking care of the issue in proper way. Notwithstanding missing information data has officially ended up being agreeable in learning based systems.

Fig. 22. Real and reactive power of converter1 and converter2

### Special Issue-5 ISSN: 2349-6495(P) | 2456-1908(O)

Fig. 23. The performance of the dual-converter system during 10% grid voltage sags, with 10.03% THD.

Grid current

#### Conclusion

At the point when a single multi-useful interfacing converter is received to compensating generation the harmonic current from nearby nonlinear burdens, the nature of supply voltage to neighborhood load can barely be enhanced in the meantime, specific when the fundamental network voltage is blended. This paper examines a novel composed voltage and current controller for double

converter system in which the nearby load is straightforwardly associated with the shunt capacitor of the primary converter. With the setup, the nature of supply voltage can be improved by means of a direct shut circle harmonic voltage control of filter capacitor voltage. In the meantime, the harmonic current brought on by the nonlinear load and the principal converter is repaid by the second converter. Consequently, the nature of the network current and the supply voltage are both essentially progressed. To lessen the computational heap of DG interfacing converter, the organized voltage and current control without utilizing load current/supply voltage harmonic extractions or stage bolt loops is produced to acknowledge to composed control of parallel converters.

#### REFERENCES

[1] B. Singh, K. AI-Haddad, A. Chandra, "A review of active filters for power quality improvement," *IEEE Trans. Ind. Electron.*, vol. 46, no. 5, pp. 960 - 971, May. 1999.

[2] P. Acuna, L. Moran, M. Riv generation, J. Dixon, and J. Rodriguez, "Improved active power filter performance for renewable power gen generation tion systems," *IEEE Trans. Power Electron.*, vol. 29, no.2, pp. 687-694, Feb. 2013.

[3] Y. W. Li, F. Blaabjerg, D. M. Vilathgamuwa, and P. C. Loh, "Design and Comparison of High Performance Stationary-Frame Controllers for DVR Implementation," *IEEE Trans. Power Electron.*, vol. 22, pp. 602-612, Mar. 2007.

[4] C. Meyer, R. W. DeDoncker, Y. W. Li, and F. Blaabjerg, "Optimized Control Strategy for a Medium-Voltage DVR –

Theoretical Investigations and Experimental Results," *IEEE Trans. Power Electron.*, vol. 23, pp. 2746-2754, Nov. 2008. [5] F. Blaabjerg, Z. Chen, and S. B. Kjaer, "Power electronics as efficient interface in dispersed power gen generation tion systems," *IEEE Trans. Power Electron.*, vol. 19, pp. 1184-1194, Sep. 2004.

[6] A. Timbus, M. Liserre, R. Teodorescu, P. Rodriguez, and F. Blaabjerg, "Evaluation of current controllers for distributed power gen generation tion systems," *IEEE Trans. Power Electron.*, vol. 24, no. 3, pp. 654–664, Mar. 2009.

[7] J. M. Guerrero, L. G. Vicuna, J. Matas, M. Castilla, and J. Miret, "A wireless controller to enhance dynamic performance of parallel inverters in distributed gen generation tion systems," *IEEE Trans. Power Electron.*, vol. 19, no. 4, pp. 1205-1213, Sep, 2004.

[8] J. M. Guerrero, J. C. Vasquez, J. Matas, L.G. de Vicuna, and M. Castilla, "Hi generation rchical control of droopcontrolled AC and DC microgrids - A gen generation 1 approach toward standardization," *IEEE Trans. Ind. Electron.*, vol. 55, no. 1, pp. 158 - 172, Jan. 2011.

[9] J. He and Y. W. Li, "Analysis, design and implementation of virtual impedance for power electronics interfaced distributed gen generation tion," *IEEE Trans. Ind. Applicat.*, vol. 47, no. 6, pp. 2525-2038, Nov/Dec. 2011

[10] Q. Zhang, "Robust droop controller for accurate proportional load sharing among inverters op generation ted in parallel," *IEEE Trans. Ind. Electron.*, vol. 60, no. 4, pp. 1281–1290, Apr. 2013.

[11] W. Issa, M. Abusara, and S. Sharkh, "Control of transient power during unintentional islanding of microgrids," *IEEE Trans. Power Electron.*, online early access.

Puttu Ashok is pursuing his Master of Technology in Power Systems, EEE Department, S V College of Engineering, Karakambadi Road, Tirupati, and Andhra Pradesh, India.

Dr. Shaik Rafi Kiran, a PhD from Jawaharlal Nehru Technological University Anantapur, Ananthapuramu, A.P, India. He has 17 years of teaching experience. At Present Dr. Shaik Rafi Kiran serving as a Professor and Head of the department of Electrical and Electronics Engineering in Sri Venkateswara college of Engineering (SVCE),Tirupathi, Andhra Pradesh. He is a Life Member of ISTE. He has presented 25 research papers in reputed International Journals and Conferences .His research areas includes System Identification, Control Systems, Optimization Techniques and Power Systems. At present he is guiding two PhD scholars